AMD Zen

Zen是一種x86-64微架構,由AMD開發,2016年發表,取代Bulldozer微架構及其改進版本。該微架構是AMD重返高效能運算市場的重要產品,與舊有架構相比幾乎完全重新設計並以新工藝製作以提升效能,同時還引入眾多新特性,處理器產品以SoC或半SoC形態面市。而首款Zen微架構的處理器,核心代號「Summit Ridge」,正式品牌名稱為「Ryzen」,而中文名稱為「銳龍」,于2017年3月2日正式上市。[1][11][12][13][14]外部合作方面,超微以2.93億美金賣給中科海光的x86架構CPU使用,不過預計不會提供後續型號的授權[15]。

| 產品化 | 2017年3月2日[1] |

|---|---|

| 設計團隊 | AMD |

| 生产商 | |

| 指令集架構 | AMD64 (x86-64) |

| 制作工艺/製程 | 14 奈米(FinFET)[3] |

| 核心数量 | |

| 一級快取 | 每核心 32 KiB 資料 + 64 KiB 指令 |

| 二級快取 | 每核心 512 KiB |

| 三級快取 | 每個CCX 4~8 MiB |

| CPU主频范围 | 2.0 GHz 至 4.0 GHz |

| CPU插座 |

|

| 應用平台 | 桌上型電腦、笔记本、服务器、工作站等 |

| 核心代號 |

|

| 使用的處理器型號 | |

| 上代產品 | Excavator微架構 |

| 繼任產品 | Zen 2[10] |

| 35~65 W(筆電/桌面APU) 65~180 W(桌面/服务器CPU) 12~35 W(低功耗APU) | |

概覽

首個基於Zen微架構的系統展示平台在2016年的E3消費電子展上現身,而架構的細節,則是到了同年英特爾開發者論壇正舉行時,在其舉行地點對面的街區上公佈。不同於使用將近6年的並且在各種小修小補和僅更新了一次製作工藝的Bulldozer微架構,Zen微架構由曾經領隊設計K6/K7/K8架構、2012年回歸AMD的Jim Keller帶隊操刀另行開發,並且直接使用14nm節點FinFET製程,著重於提升每個CPU核心的效能,最初目標是比當時預期的Bulldozer微架構最終形態時每時鐘週期指令數(IPC)高出40%。此外處理器連接界面、插座、記憶體支援等等都力圖更新到最新規格。[16]除了效能和功能上的提升以外,還試圖以AMD APU產品線的經驗將新架構系統平台的體積縮小,令單一一顆CPU可以以SoC形態出現並支援常見的匯流排規格(包括PCIe、SATA、USB等)。[17][18]加之此前發表的300系列晶片組、Socket AM4/Socket FP4插座、對DDR4的支援等,這些使得AMD可以令Zen微架構只需些少修改即可涵蓋當前的筆電、小尺寸PC乃至桌上型電腦、工作站、伺服器(特別是高運算密度的雲端運算平台)等運算系統平台。[19][20][21]2017年中發表的AMD Epyc系列,取代Opteron成為AMD面向企業應用(特別是雲端運算)的企業級CPU系列,並且可作為無需南橋晶片的半SoC化產品。[22]

架構設計

%2540Summit_Ridge%2540Ryzen_3_1200%2540YD1200BBM4KAE_UA_1724PGT_9GW9105S70241_Stack-DSC01422-DSC01535_-_ZS-retouched_(35686281913).jpg.webp)

- 32KB (L1d)(8路)、64KB (L1i)(4路),可以直接回寫(write-back),降低延時、加大頻寬,此前的是先通過指針回寫至記憶體再更新一級快取(write through),與Bulldozer模組相比增大兩倍頻寬

- 同步多執行緒(SMT),一個CPU核心可執行兩個執行緒。該特性此前在IBM POWER、英特爾(超執行緒)及甲骨文的SPARC上提供[26]放棄Bulldozer微架構的(CMT)設計

- 每核心4個算術邏輯單元(ALU)和兩個位址生成單元(AGU)/載入存儲單元

- 因不再使用Bulldozer模組化設計,浮點運算單元(FPU)不再由兩組整數ALU叢集共享,改回傳統的1顆物理核心1組浮點運算單元(每組4個128bit FPU單元,可組成兩個256bit FPU 單元來操作)[27]

- 512KiB 二級快取(L2)為每個CPU核心獨占,與Bulldozer模組相比增大兩倍頻寬

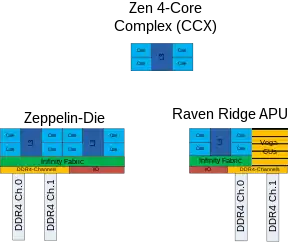

- 三級快取(L3)為每4個CPU核心組成的CCX模組(CPU核心複合體,其中的CPU核心仍可單獨關閉[28])共用,CCX之間通過Infinity Fabric互聯實現快取一致性,比Bulldozer模組快5倍

- 大型宏操作快取

- 每個SMT核心每時鐘週期能最多分派6個微操作(整合6個整數操作和4個浮點操作)[29][30]

- 更大的撤回、載入、存儲隊列

- PTE(分頁表條目)接合,可將4KiB的分頁表合併至32KiB的分頁尺寸上

- 智慧型預取

- 4個解碼單元,每個時脈週期可以解碼4條x86指令

- 使用帶Indirect Target Array的散佈型感知器的增強型分支預測,類似於Bobcat微架構的[31],AMD工程師Mike Clark稱其可與人工神經網路相比[32];其優勢是對於幽靈漏洞的防範能力較佳。

- 分支預測器在指令/資料抓取階段解除耦合

- 為修改堆疊指針而專用的堆疊引擎(堆疊暫存器),類似英特爾Haswell微架構/Broadwell微架構的設計[33]

- 搬移限制,降低物理資料搬移以降低功耗

- 高效能硬體隨機數產生器,支援RDSEED。RDSEED是英特爾在Boardwell微架構上實作的硬體隨機數產生器的調取指令[34]

- 支援x86/AMD64、x87、MMX(+)、SSE/SSE2/SSE3/SSSE3/SSE4.1/SSE4.2/SSE4a、AVX/AVX2、FMA3、CVT16/F16C、AES、SHA、ADX等指令集,移除XOP、FMA4、LWP、TBM等甚少使用的指令集支援

- 支援SMAP、SMEP、XSAVEC/XSAVES/XRSTORS、XSAVES、CLFLUSHOPT、CLZERO以及ADCX指令集[34]

- 支援AMD-V、IOMMU虛擬化技術

- 新的时钟门控

- 基於HyperTransport擴展的高頻寬低延時的Infinity Fabric互聯架構,在基於Zen的處理器上大量使用的NUMA結構之瓶頸可被大幅緩解

- 消費級系統支援雙通道DDR4-2666的記憶體配置規格,企業級系統最高支援八通道並且帶ECC的DDR4記憶體,不支援DDR3

- AMD SenseMI,[35][36][37]使用AMD Infinity Control Fabric提供以下功能:

- SoC設計,提供傳統南橋和北橋晶片的功能(包括PCIe、SATA/AHCI、NVMe、USB),不過AMD還是發表了其委託祥碩設計的300系列晶片組

- Socket AM4插座[35]

- 對GCC、LLVM等編譯器做了性能最佳化

處理器產品

除了2017年3月販售的Ryzen以外,主流消費級AMD APU產品線也更新到Zen微架構了,新版AMD APU預計2017年下半年開賣,[9]而伺服器及工作站用的Opteron系列,則是更名為EPYC[39],預計2017年第二季度以後出貨。[40]

目前出貨的Zen微架構的處理器均為GlobalFoundries在美國紐約州的Fab 8廠製造,製程工藝技術來自GF與三星電子旗下晶圓廠合作的14nm LPP[41]。受制於GF的生產能力,AMD在2017年初以一億美元的代價修訂與GF的合同,不再排除讓三星、台積電代工製造的可能,不過這將在未來的7nm製程節點上開始。[42]

Ryzen系列

2017年3月初至4月中,Ryzen 7、Ryzen 5系列處理器正式上市,Ryzen 7為8核心16執行緒的桌上型電腦處理器,Ryzen 5則是有6核心12執行緒和4核心8執行緒兩種規格,基準時脈從3 GHz ~ 3.6 GHz不等,均支援雙通道DDR4記憶體,擁有最多24條PCIe通道。

早期Ryzen系列的DDR4記憶體支援度有相容性問題,記憶體只能以較低的速率、時序參數運行。不過隨著2017年3月、4月的數次AGESA韌體的更新,已經大有改善,最高能支援至DDR4-3200規格。[43][44]

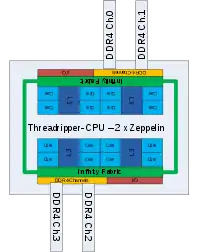

AMD也發表了極致效能級別的產品Ryzen ThreadRipper(线程撕裂者),由Epyc的NUMA結構衍生而來,目前最新版本ThreadRipper PRO 3995WX最高64核心128執行緒規格,支援八通道記憶體(由四個雙通道記憶體控制器提供支援)最高可擴充到2TB。本次也是繼AMD Quad FX平台以來第二次面向消費級市場推出NUMA結構的電腦系統平台,不過這次AMD將多顆處理器整合到一塊處理器基板上,僅需一個處理器插座。[45]

APU產品線

2017年5月17日AMD公佈了行動版Ryzen處理器,均為自家的APU產品。本次公佈的CPU規格是,4核心8執行緒、每核心 512KB 的 L2 Cache、所有CPU核心共用 4MB L3 Cache,基準時脈有 1.9 GHz、2 GHz、3 GHz的配置,最高加速時脈可達 3.3 GHz;而GPU則是採用與代號「Vega」GPU相同的架構,11組CU共704個ALU,核心時脈800MHz左右。[46]

EPYC系列

2017年5月17日AMD在財務分析報告會上宣布,基於Zen微架構的伺服器/工作站用CPU,另立Epyc品牌取代原來Opteron品牌。[39]主攻高密度雲端運算等企業應用。[22]

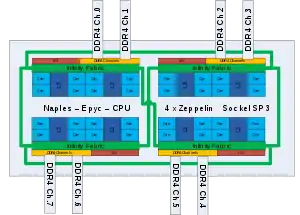

最高規格是核心代號「Naples」的多晶片模組,由4顆8核心16執行緒的處理器晶片做在一塊處理器PCB上,所以一共擁有4×8個CPU核心,4×16執行緒,晶片之間採用Infinity Fabric連接。處理器採用Socket SP3 LGA封裝,支援雙處理器,每顆處理器支援八通道DDR4記憶體(由每顆晶片提供雙通道支援),每顆處理器擁有高達64條PCIe 3.0通道,處理器之間也使用Infinity Fabric連接。[39]

由於處理器晶片是已經內建SATA/SATA Express控制器、USB控制器、時鐘電路等傳統上由南橋晶片提供的功能,針對高密度伺服器的主機板可更利用海量的PCIe通道增加網路處理元器件、RAID陣列控制器等而無需南橋晶片,必要的也就一顆顯示輸出用GPU,也是x86架構平台首次對伺服器市場推出高度整合化的半SoC化處理器。[22]不過,也由於處理器本身的多晶片模組設計,相當於一顆NUMA結構的4路處理器平台,需要軟體開發做更進一步的針對NUMA結構的最佳化調適,尤其於工作站用途時,不過市面上並不缺少NUMA的使用範例,Intel在企業級平台上也是大量使用。[45]

效能表現

從多數媒體的首發效能評測而言禪架構比起推土機架構獲得了廣泛的好評,首發產品Ryzen 7系列的每個CPU核心的效能及多執行緒效能已經達到Intel Haswell/Boardwell微架構在同時脈下的水準,能源效率則更佳,多執行緒的需求是Ryzen的優勢,其競爭對手的處理器產品採用舊一代的架構時的預設時脈也不會如此高。[47][48]但不足之處是,一來受制於製造工藝,最高時脈及能源效率不如對手英特爾最新的Skylake/Kaby Lake微架構的產品(Intel的14奈米製程,在許多方面表現的都優於其他晶圓廠的14/16nm製程),儘管Skylake/Kaby Lake微架構同時脈下效能與Haswell/Boardwell微架構的相比僅5%的效能差別[49][50];二來是長久以來AMD高效能系統平台的缺席、市佔劣勢,間接導致不少軟體對AMD處理器的效能最佳化不良,特別是一些電腦遊戲(一些遊戲效能測試結果顯示似乎這些遊戲並不適應AMD的同步多執行緒,出現效能不升反降的情況,以網路遊戲為重災區)[51][52][53]。

目前英特爾主要以製造工藝優勢和預設高時脈優勢與AMD拉開差距,為維持x86處理器的效能領導地位,英特爾推出了Core i9系列,市場定位相當於以往的Core i7極致版,但規格更為誇張(特別是時脈參數上,儘管耗電和發熱量上也有所增長)。針對企業級市場打造的EPYC,則在巨量資料處理以及高效能運算上樂勝英特爾的Xeon系列,但是在資料庫處理方面則不敵對手。[54]

Ryzen並沒有熔毀漏洞、幽靈漏洞的問題也比較輕微,競爭對手Intel修正這些漏洞所造成的效能損失,讓Ryzen在許多需求的競爭力提高。

有第三方x86-64指令集程式最佳化指導機構Anger,推出了針對Zen微架構處理器的源碼最佳化建議指導。[55]

Zen+

| 產品化 | 2018年4月 |

|---|---|

| 設計團隊 | AMD |

| 生产商 | |

| 核心数量 |

|

| 一級快取 | 每核心 32 KiB 資料 + 64 KiB 指令 |

| 二級快取 | 每核心 512 KiB |

| 三級快取 | 每個CCX 8 MiB |

| CPU插座 | |

| 應用平台 | 桌上型電腦、工作站等 |

| 核心代號 | |

| 使用的處理器型號 |

|

| |

Zen+是Zen的改進型微架構,[58]首款基於Zen+的處理器於2018年4月發表。[59]

改進之處

Zen+微架構的處理器使用了GlobalFoundries的「12奈米」LP(Leading Performance)工藝製作,[60]該製程工藝實際上是同廠14奈米LPP工藝的改良版,重在提高單位面積下電晶體的數量(即同等電路下減少晶片面積),而Zen+相較於Zen而言沒有大變動,電晶體數量也是幾乎一樣。[61]有第三方媒體對基於Zen+的Ryzen 7進行實測,發現除了晶片面積有所減少以外,相較於第一代也有小幅的時脈提升及同等效能下功耗的下降,[62][61]但這個也與AMD對Zen的電源管理有改善有關,主要是對AMD SenseMI電源管理的調整改善,令CPU電源管理模組更快響應CPU的負荷需要,並且在有負荷時CPU核心的時脈比此前Zen的更能維持高時脈,特別是XFR2,還進一步改進了檢測單個CPU核心在當前最高工作溫度下的最高時脈的特性。[63]

除了換用更新的製程以及對CPU電源管理的改善外,還有:[64]

- 降低對快取、記憶體存取時所需的時鐘週期

- 提升快取頻寬

- 更佳的記憶體相容性以及更高效能參數的記憶體支援(原生支援DDR4-2933,XMP/AMP支援下更達DDR4-3400+)

這些改進使得Zen+相較於Zen而言同時脈下每時鐘週期能處理多3%的指令數量,最高時脈也有6%的提升,最終大約取得10%左右的效能提升。[61]

配套的晶片組更新至400系列,不過原先300系列的通過AGESA EFI韌體更新後(若廠商提供)也可以使用基於Zen+的處理器。

Zen 2

首批採用Zen 2微架構的CPU產品於2019年7月發表,Zen 2顯著改善了效能。

Zen 3

首批採用Zen 3微架構的CPU產品於2020年10月8日發布。

相關

- AMD Zen+架構

- AMD Zen 2微架構

- AMD Zen 3微架構

- AMD FCH

- Radeon 500系列

參考文獻

- . AMD. 2 March 2017 [4 March 2017]. (原始内容存档于2017-06-09).

- . bitsandchips. [2018-04-14]. (原始内容存档于2018-04-14).

- . ExtremeTech. [2016-11-19]. (原始内容存档于2016-12-07).

- Anthony, Sebastian. . Ars Technica. 18 August 2016 [18 August 2016]. (原始内容存档于2016-11-21).

- . [2016-11-19]. (原始内容存档于2016-05-02).

- . TechPowerUp. [2016-11-19]. (原始内容存档于2016-03-02).

- Ryan Smith. . AnandTech. 6 May 2015 [2016-11-19]. (原始内容存档于2015-05-08).

- . 編譯整理自twitter@CanardPC/Benchlife. [2018-04-14]. (原始内容存档于2018-04-14).

- Kampman, Jeff. . Tech Report. 18 August 2016 [18 August 2016]. (原始内容存档于2016-11-18).

- Bo Moore. . pcgamer. [2016-11-19]. (原始内容存档于2016-10-30).

- . bit-tech. 11 September 2014 [15 December 2014]. (原始内容存档于2015-04-02).

- Mujtaba, Hassan. . WCCF Tech. May 5, 2014 [January 15, 2015]. (原始内容存档于2015-03-10).

- . PCGamesN. 2017-02-14 [2017-02-20]. (原始内容存档于2017-02-11) (英语).

- . techbang.com. [2017-03-27]. (原始内容存档于2017-03-27).

- . [2021-04-14]. (原始内容存档于2021-04-17).

- Brad Chacos. . PCWorld. 8 January 2016 [2017-03-27]. (原始内容存档于2017-02-02).

- . PCWorld. [2017-03-08]. (原始内容存档于2017-02-06) (英语).

- Cutress, Ian. . Anandtech. 18 August 2016 [22 March 2017]. (原始内容存档于2017-03-22).

- . wccftech.com. [2017-03-30]. (原始内容存档于2017-03-30).

- 郑双艳. . 騰訊數碼. 2015-02-23 [2015-02-24]. (原始内容存档于2015-02-23) (中文(中国大陆)).

另外,在封装接口方面,Zen架构将会实现与现有ARM处理器的接口兼容和互换。AMD在去年发布ARM架构处理器时就宣称将与以后的处理器实现接口的兼容,看来AMD是早有准备。而如果这一技术能够实现,那么对于企业级用户来说,这将是一个巨大的进步,对ARM阵营也将是一个强心剂。

- . Softpedia. 28 January 2015 [31 January 2015]. (原始内容存档于2015-03-10).

- . TechNews 科技新報. [2017-08-25]. (原始内容存档于2017-08-25).

- . techspot.com. [2015-05-12]. (原始内容存档于2015-05-11).

- . techreport.com. [2015-05-12]. (原始内容存档于2015-05-09).

- Anton Shilov. . KitGuru. 11 September 2014 [1 February 2015]. (原始内容存档于2016-06-04).

- . [2017-03-27]. (原始内容存档于2016-03-04).

- Clark, Mike. (PDF). AMD: 7. [2017-03-27]. (原始内容存档 (PDF)于2016-11-26).

- . [2018-04-14]. (原始内容存档于2018-04-14).

- Mujtaba, Hassan. . WCCFtech. [23 August 2016]. (原始内容存档于2016-08-25).

- Walrath, Josh. . PC Perspective. [13 March 2017]. (原始内容存档于2017-10-12) (英语).

- Jiménez, Daniel. (PDF). Texas A&M University. (原始内容存档 (PDF)于2016-09-19).

- Williams, Chris. . The Register. (原始内容存档于2017-02-24).

- Fog, Agner. (PDF). Technical University of Denmark. (原始内容存档 (PDF)于2017-03-28).

- . Phoronix. 17 March 2015 [17 March 2015]. (原始内容存档于2017-03-08).

- Cutress, Ian. . anandtech.com. 2017-03-02 [2017-03-16]. (原始内容存档于2020-03-18).

- Walton, Mark. . arstechnica.com. 2017-03-02 [2017-03-03]. (原始内容存档于2020-02-03).

- Alcorn, Paul. . tomshardware.com. 2017-03-02 [2017-03-03].

- Verry, Tim. . PC Perspective. 2017-03-04 [2017-03-04]. (原始内容存档于2019-03-31).

- . [2017-05-17]. (原始内容存档于2017-05-19).

- . expreview.com. [2017-03-27]. (原始内容存档于2017-03-27).

- . [2017-04-28]. (原始内容存档于2017-10-24).

- . 中時電子報. [2017-10-24]. (原始内容存档于2017-10-25) (中文(臺灣)).

- . [2017-05-17]. (原始内容存档于2017-04-09).

- . [2017-05-17]. (原始内容存档于2017-05-14).

- . [2017-08-25]. (原始内容存档于2017-08-25) (中文(臺灣)).

- . [2017-05-17]. (原始内容存档于2017-05-19).

- . techbang.com. [2017-03-27]. (原始内容存档于2017-03-27).

- . expreview.com. [2017-03-27]. (原始内容存档于2017-03-27).

- . pconline.com.cn. [2017-04-08]. (原始内容存档于2017-04-03).

- . expreview.com. [2017-04-08]. (原始内容存档于2017-04-03).

- . [2018-04-14]. (原始内容存档于2018-04-14).

- . expreview.com. [2017-03-27]. (原始内容存档于2017-03-27).

- . techbang.com. [2017-03-27]. (原始内容存档于2017-03-27).

- De Gelas, Johan; Cutress, Ian. . Anandtech. 11 July 2017 [11 July 2017]. (原始内容存档于2017-08-26).

- . [2017-05-23]. (原始内容存档于2017-05-17).,原載於Test results for AMD Ryzen (页面存档备份,存于)

- Cutress, Ian. . Anandtech. 5 June 2018 [6 June 2018]. (原始内容存档于2018-06-12).

- Alcorn, Paul. . Tom's Hardware. 13 April 2018 [13 April 2018].

- Cutress, Ian. . Anandtech. 8 January 2018 [8 January 2018]. (原始内容存档于2018-06-12).

- Bright, Peter. . Ars Technica. 8 January 2018 [9 January 2018]. (原始内容存档于2020-02-03).

- . ExtremeTech. 2017-09-22 [2018-02-04]. (原始内容存档于2018-02-05) (美国英语).

- Cutress, Ian. . Anandtech. 19 April 2018 [30 April 2018]. (原始内容存档于2018-06-12).

- Kampman, Jeff. . Tech Report. 8 January 2018 [8 January 2018]. (原始内容存档于2018-06-13).

- Leather, Anthony. . Forbes. 7 January 2018 [9 January 2018]. (原始内容存档于2018-06-12).

- Mah Ung, Gordon. . PC World. 7 January 2018 [9 January 2018]. (原始内容存档于2018-01-13).

外部連結

| 维基共享资源上的相关多媒体资源:AMD Zen |

- “Zen” 核心架构(页面存档备份,存于)(简体中文)

- 【Arstechnica】Zen架构详解(页面存档备份,存于)

- 卧虎藏龙,锐龙 AMD Ryzen 7 1800X评测汇总(页面存档备份,存于)(简体中文)