微架構

微架構(英語:),也被叫做計算機組織,微架構使得指令集架構(ISA)可以在處理器上被執行。指令集架構可以在不同的微架構上執行。 計算機結構是一門探討微架構與指令集兩者互動的一門學問。

和指令集架構的關係

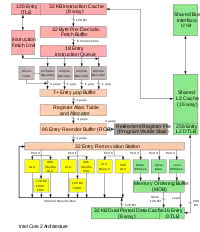

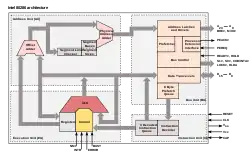

指令集架構是指在處理器內被處理的程式,指令集架構為組合語言的設計師和編譯器所見。指令集架構包含execution model,暫存器,地址以及資料格式。微架構包含處理器內部的構成以及這些構成起來的部分如何執行指令集架構。微架構通常被表示成流程圖,以描述機器內部元件的連結狀況,從一個閘或是暫存器,到算術邏輯單元(ALU)。圖上分布著資料路徑(可以顯示資料在微架構的位置)以及控制路徑(顯示資料該被什麼指令所處理)。

每個微架構的的元件都被表示成藉數個邏輯閘所建構而成的工具。每個邏輯閘都被表示成藉電晶體建構成的零件。擁有不同微架構的機器可能擁有相同的指令集架構,因此可以執行相同的程式。由於半導體科技的進步,新型的處理器可以以較快的速度執行相同的指令集架構。

微架構的概念

现时,流水线数据路徑是微架構中最常被使用的数据路徑。這種作法也被普遍的用於微處理器,微控制器,以及数字信号处理器。流水线的結構允許多個指令在同一時間執行,不同的指令在微架構不同的位置執行。流水线分有好幾個不同的階段(stage),這些階段是微架構的基礎。這些階段包含取指令,译码,執行指令,以及將資料寫回。一些結構還包含其他階段,像是對記憶體做存取的動作。流水线是微架構其中一項主要的工作。執行單元也是微架構的基本元件。執行單元包含算術邏輯單元(ALU),浮點運算器(FPU),load/store單元,分支預測,以及SIMD。這些單元在處理器內進行計算。執行單元的數量,他們的延迟(記憶體存取資料的時間)及吞吐量(將資料存到或是讀取出記憶體的速度)影響微架構的效能。

執行速度

上面的步驟看起來簡單,但階層記憶體使這些步驟變得複雜,階層記憶體包含快取,主記憶體,以及非揮發性的記憶體,例如硬碟(這是指令和資料儲存的地方),總是比處理器處理資料的速度慢。步驟(2)常常導致lengthy(在CPU內)delay,這種延遲是在数据通過匯流排時產生。一直以來,一個不變的目標是在同一時間內執行更多指令,以提升程式執行的效率。這導致邏輯和電路設計變得更複雜。一開始,只有大型電腦和超級電腦使用這種技術,因為這種技術需要大量的電路。當半導體產業發展起來後,這樣的技術被加裝在單一的半導體晶片上。詳見摩爾定律(集成電路可容納的晶体管數量,每二年增加一倍)。

指令集的選擇

指令集從過去以來不斷的變化,從一開始的簡單到後來的複雜。最近,load-store結構,VLIW以及EPIC是最普遍的指令集。結構處理data parallelism的方法包括SIMD以及向量。一些指令集,例如CISC;多早期的裝置使用"CISC"。

然而,對指令集架構的選擇可能會對實作高效能的機器產生大的影響。發展RISC處理器是一個好的策略,可以將指令給簡化。這樣的指令容易在管線內被擷取,解碼與執行,由於指令頻繁的被使用,快取便被頻繁的使用,這樣就使記憶體存取的時間降低。

流水线(pipeline)

在目前,能夠最有效的提升效能的方法就是流水线。早期的處理器是等一個指令執行完所有步驟後,然後才輪到下一個指令執行。大部分的電路在某一個步驟結束後就處在閒置的狀態,例如,對指令進行解碼的電路在指令進入執行階段後就處於閒置狀態。

流水线化的電路藉由允許多個指令在同一時間,在電路上不同的位置進行不同的工作。例如,處理器可以在最後一個指令等待結果寫回時對另一個指令解碼。這使得處理器在同一時間可以處理四個指令,使處理器的效能增加了四倍。

RISC藉由將每個階段分割清楚並讓每個階段都花費一樣的時間執行來讓流水线變小和變得容易建構—每個階段花費1個cycle的時間。處理器使用了有如工廠流水线的設計,當指令由一邊進來的同時就有另一個指令從另一邊出去。由於RISC流水线是降低複雜度的設計,使得流水线核心跟指令快取可以被裝置在同一個芯片內,這是精簡指令集較為快速的原因。早期的裝置,例如SPARC和MIPS比Intel和Motorola的CISC還快10倍。

几種典型的微架構

Intel

AMD

- K5 - AMD的首个原创微架构。K5基于Am29000的微架构,并且添加了一个x86的解码器。即使这个设计的原理和Pentium Pro相同,而实际性能更像是Pentium。

- K6 - K6并非基于K5,而是基于当时已经被AMD所收购了的NexGen所设计的Nx686处理器,K6的针脚兼容Intel Pentium。

- K7 - 是AMD Athlon和Athlon XP的微架构。

- K8微架构 - 全球首款x86-64處理器,集成了記憶體控制器(Integrated Memory Controller),采用HyperTransport技術,增加了SSE指令集。后期的K8增加了SSE3。K8在2003年4月22日上市。HyperTransport取代了传统的前端总线,让CPU直接和內存链接。

- K9 - 被取消。

- K10微架构 - 代号为Barcelona ,是AMD系列的第十代微架构,最多内置四个核心,共享Level 3 Cache第三级缓存,128位浮点单元,支援AMD-V Nested Paging Virtualization和HyperTransport 3.0。

- Bulldozer - 是继K10之后,使用AMD M-SPACE模块化设计方法(modular design methodology)的微架构。Bulldozer是为功耗在10W至100W类别的处理器而设计,应用了XOP,FMA和CVT16指令集,并且部分產品整合了GPU核心(AMD APU)。

- Zen+微架構 - AMD在2018年推出的微架構,CPU晶片採用12納米製程。

参考文献

- 《计算机科学技术百科全书》(第二版). 作者:张效祥. 出版社:清华大学出版社,2005年. ISBN:7302105944, 9787302105947