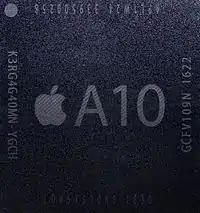

Apple A10 Fusion

Apple A10 Fusion(融合)是蘋果公司設計的64位系統單晶片(SoC),由台积电代工生产,为16 nm制程。[3]這款晶片於2016年9月7日發佈,首先被搭載於iPhone 7和iPhone 7 Plus智能手機中。[4][5]

| |

| 產品化 | 2016年9月7日至現在 |

|---|---|

| 設計團隊 | Apple Inc. |

| 生产商 | |

| 微架構 | Hurricane,ARMv8-A兼容 |

| 指令集架構 | A64, A32, T32 |

| 制作工艺/製程 | 16纳米(nm) |

| 核心数量 | 2+2 |

| 一級快取 | 126 kB 指令 + 126 kB 數據 |

| 二級快取 | 3MB |

| 三級快取 | 4MB |

| CPU主频范围 | 至 2.34 GHz[2] |

| 應用平台 | 手機 |

| 上代產品 | Apple A9、Apple A9X |

| 繼任產品 | Apple A11 Bionic |

| 相關產品 | Apple A10X Fusion |

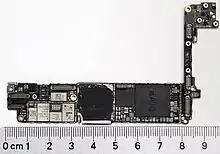

在iPhone 7上的Apple A10 SoC 主機板

概覽

A10 Fusion是基於ARM架構下,蘋果首款使用big.LITTLE組態的四核心SoC[6],包括兩枚高效能核心及兩枚低功耗核心,電晶體數量為33億個。[7]不過A10 Fusion採用就是big.LITTLE內核內建切換器方式(In-kernel switcher,IKS)而不是高通驍龍820採用的HMP方式:一個低功耗核心和一個高效能核心組成一對,共用L2快取,作為一個虛擬CPU核心(在iOS內核中根據負載需要切換),每個虛擬CPU核心在同一時間點上只有高效能核心或低功耗核心在運作,因此在iOS中僅能看到兩顆處理器核心。[8][9]

A10的高效能CPU核心代号为“飓风”(Hurricane),而低功耗CPU核心代號為「微風」(Zephyr),均為蘋果公司自行設計的ARMv8相容微架構。蘋果宣稱此晶片較上代在CPU效能提升了40%,在圖形運算提升了50%。

参考文献

- . [2016-10-02]. (原始内容存档于2016-09-20).

- Cunningham, Andrew. . Ars Technica. 13 September 2016 [14 September 2016]. (原始内容存档于2016-09-29).

- Ko, Cheng-Ta; Yang, Henry; Lau, John; Li, Ming; Li, Margie; Lin, Curry; Lin, J. W.; Chang, Chieh-Lin; Pan, Jhih-Yuan; Wu, Hsing-Hui; Chen, Yu-Hua. . Journal of Microelectronics and Electronic Packaging. 2018-10-01, 15 (4). ISSN 1551-4897. doi:10.4071/imaps.734552 (英语).

- . [2016-09-11]. (原始内容存档于2016-09-08).

- . [2016-09-11]. (原始内容存档于2016-09-09).

- . [2017-04-28]. (原始内容存档于2017-08-19).,注:蘋果公司一直否認該設計是ARM的big.LITTLE組態而是自行設計配置,但ARM公佈的big.LITTLE實現方式中有和蘋果公司描述的實現方式一致的方式(In-kernel switcher),參見big.LITTLE#內核內建切換器(CPU遷移)一章節

- . TechCrunch. [7 September 2016]. (原始内容存档于2016-09-11).

- . [2017-04-28]. (原始内容存档于2018-01-12).

- . [2017-04-28]. (原始内容存档于2017-06-29).原載於expreview.com (页面存档备份,存于)

This article is issued from Wikipedia. The text is licensed under Creative Commons - Attribution - Sharealike. Additional terms may apply for the media files.