系統匯流排

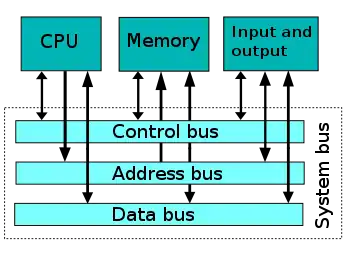

系統匯流排(英語:)是一個單獨的電腦匯流排,是連接電腦系統的主要元件。這個技術的開發是用來降低成本和促進模組化。系統匯流排結合資料匯流排的功能來搭載資訊,位址匯流排來決定將資訊送往何處,控制匯流排來決定如何動作。雖然系統匯流排於1970年代至1980年代廣受歡迎,但是現代的電腦卻使用不同的分離匯流排來做更多特定需求用途。

背景

許多早期的電子式計算機都以1945年所公布的《EDVAC報告書的第一份草案》為基礎。在此份報告中有著為人所熟知的范紐曼型架構,一個中央控制單元和算術邏輯單元被與電腦記憶體和輸入輸出功能一起組合形成一個儲存程式計算機。[1]這份報告揭示了計算機的通用結構與理論模型,然而此一模型並未付諸實行。[2]很快的,有設計將控制單元與算術邏輯單元整合起來而成為後來為人所熟知的中央處理器。

在1950年代到1960年代,計算機的建構特別的風行。舉例來說,中央處理器、記憶體與輸入輸出單元的元件中,將其中的每個或多個元件用導線所連接。工程師們使用一般性標準化導線綑綁技術並延伸其觀念而成為迴路基板,進而將印刷電路板應用於早期的機器裡。

「匯流排」這個名稱早先就已經被使用於母線,它乘載並輸送電力到電子機器的不同部分的元件,包含早期的機械式計算器。[3]

積體電路的出現極大的縮小了計算機元件的大小,而且匯流排也變得更標準化。標準化模組可以用更有秩序的方式來連接,也更容易開發與維護。

描述

為了提供更多低成本的模組化元件,記憶體與輸入輸出匯流排(和所需的控制與電力匯流排)有時會被組合成單獨一體的系統匯流排。[4]電腦要小到可以塞進一個櫃子中,模組化與成本就變得很重要(就如同顧客對於降價的期待)。迪吉多使用大量生產迷你電腦來進一步降低成本,將存儲器映射輸入輸出放入記憶體匯流排,如此一來,裝置就可以對應到記憶體中的位置。在大約1969年時,這被實現在PDP-11的Unibus中,排除了分離式輸入輸出匯流排的需求。[5]即使電腦沒有存儲器映射輸入輸出,如PDP-8,也很快的與系統匯流排被實現出來,也允許模組被插入任意的插槽中。[6]一些作者聲稱這是新式流線型電腦架構的樣式。[7]許多早期的微電腦(一般有著單獨一顆積體電路型式的中央處理器)擁有單一的系統匯流排被建造出來,起始於大約1975年的Altair 8800電腦系統上的S-100匯流排。[8] IBM PC在1981年使用工業標準結構匯流排為其系統匯流排。早期的被動式迴路基板機型被標準放置中央處理器的主機板所取代,在系統匯流排的插槽上,可選擇性的插上子板或是擴充卡。

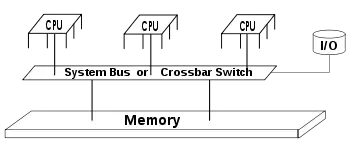

於1983年,Multibus成為電機電子工程師學會的標準規格:IEEE standard 796。[9]於1989年,昇陽電腦開發SBus用來支援更小的擴充卡。[10]實現對稱多處理的最容易的方式是插入更多的中央處理器於共享的系統匯流排上,這個方法被使用於1980年代。然而,共享匯流排很快的就變成瓶頸所在,並且有更多更複雜的連接技術被探索。[11]

雙獨立匯流排

當CPU設計發展更快的區域匯流排和更慢的周邊匯流排,Intel採用雙獨立匯流排(英語:,DIB)術語,使用外部的前端匯流排到主系統記憶體,和內部的後端匯流排於一個或多個中央處理器、CPU快取間。這個方式在1990年代中後期被使用於Pentium Pro和Pentium II產品上。[12]

主要匯流排的作用是在中央處理器、主記憶體、輸入輸出裝置間溝通資料,被稱為前端匯流排,而後端匯流排則是用來存取第二階快取。現代的個人及伺服電腦使用高效率的內部連接技術,如HyperTransport和Intel QuickPath Interconnect,當系統匯流排架構繼續使用於簡單的嵌入式微處理器時。系統匯流排也可以單獨成為一個積體電路而產生系統單晶片,例子有高級微控制器匯流排架構(AMBA),CoreConnect和Wishbone。[13]

参见

- 匯流排

- 扩展总线

参考文献

- John von Neumann. (PDF). June 30, 1945 [May 27, 2011]. (原始内容 (PDF)存档于2013年3月14日). Introduction and editing by Michael D. Godfrey, Stanford University, November 1992.

- Michael D. Godfrey; D. F. Hendry. (PDF). IEEE Annals of the History of Computing. 1993, 15 (1): 11–21. doi:10.1109/85.194088. (原始内容 (PDF)存档于2011-08-25).

- 美國專利第3,470,421号 "Continuous Bus Bar for Connector Plate Back Panel Machine Wiring" Donald L. Shore et al., Filed August 30, 1967, issued September 30, 1969.

- Linda Null; Julia Lobur. 3rd. Jones & Bartlett Learning. 2010: 36,199–203 [2013-06-14]. ISBN 978-1-4496-0006-8. (原始内容存档于2014-01-07).

- C. Gordon Bell; R. Cady; H. McFarland; J. O'Laughlin; R. Noonan; W. Wulf. (PDF). Spring Joint Computer Conference. 1970: 657–675 [2013-06-14]. (原始内容存档 (PDF)于2011-11-27).

- (PDF). Digital Equipment Corporation. 1973: 2–9 [2013-06-14]. (原始内容存档 (PDF)于2012-09-10).

- Miles J. Murdocca; Vincent P. Heuring. . John Wiley & Sons. 2007: 11. ISBN 978-0-471-73388-1.

- Herbert R. Johnson. . [2013-06-14]. (原始内容存档于2012-07-28).

- . Institute of Electrical and Electronics Engineers. 1983 [May 25, 2011]. (原始内容存档于2013-06-05).

- Edward H. Frank. . Compcon Spring '90: Intellectual Leverage. Thirty-Fifth IEEE Computer Society International Conference. February 26, 1990: 189–194. doi:10.1109/CMPCON.1990.63672.

- Donald Charles Winsor. (PDF). University of Michigan Electrical Engineering department. 1989 [2013-06-14]. (原始内容存档 (PDF)于2012-01-28). Ph.D. dissertation.

- Todd Langley and Rob Kowalczyk. (PDF). "White paper". Intel Corporation. January 2009 [May 25, 2011]. (原始内容 (PDF)存档于2011年6月7日).

- Rudolf Usselmann. (PDF). January 9, 2001 [May 30, 2011]. (原始内容存档 (PDF)于2012-03-11).